The APECS pilot line – European chiplet innovation

Prof. Dr. Albert Heuberger

The APECS pilot line – European chiplet innovation

How APECS leads the way in heterogeneous integration by providing diverse design capabilities, technologies and testing strategies for electronic components and systems on a single platform

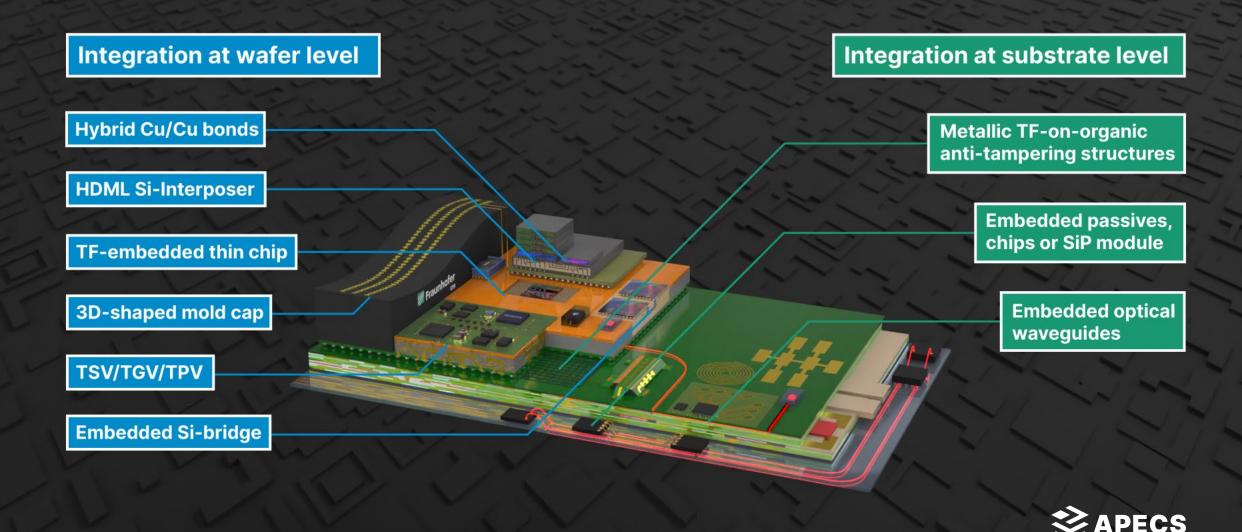

## **Examples for the integration at wafer and substrate level**

# **Application Aereas for Hetergenous Integration**

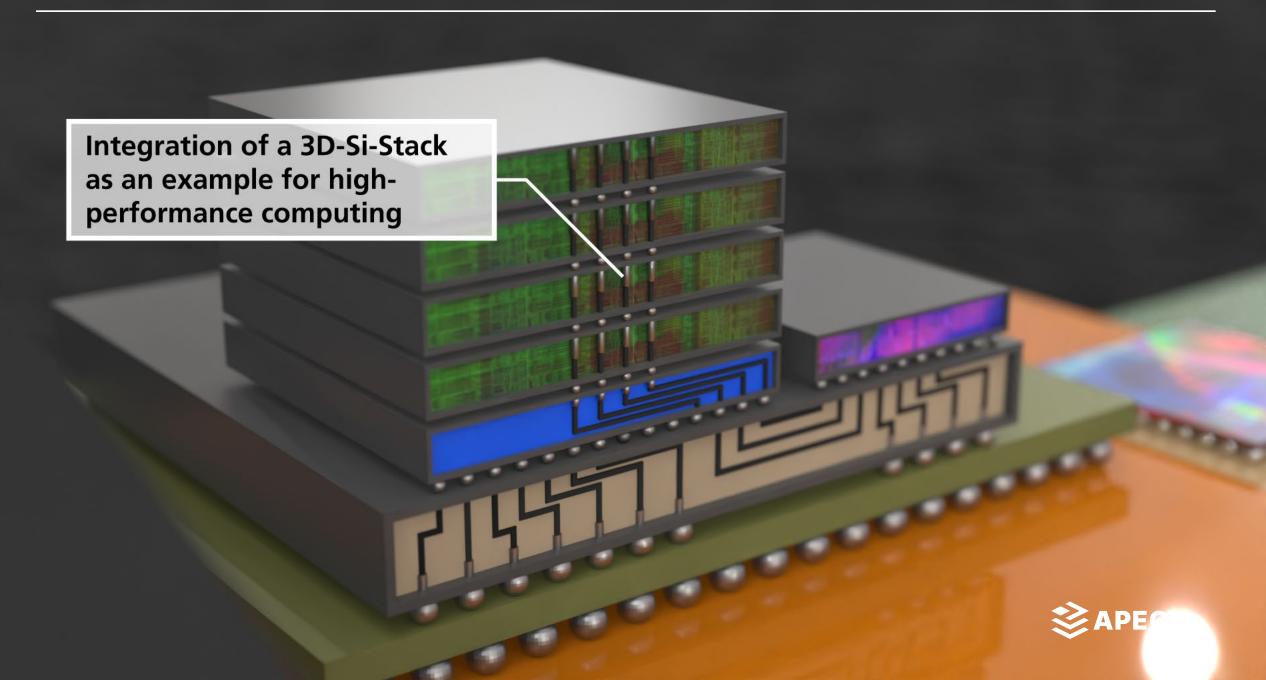

**High performance computing**

Medical & scientific instrumentation

Sensor systems

**Telecommunications**

**Industrial manufacturing**

Artificial intelligence (AI / ML)

# What are the challenges in heterogeneous integration?

### **Design complexity**

- Integrating different materials (CMOS, InP, GaAs, SiPh)

- Managing electrical and optical coupling

- Ensuring co-design efficiency and thermal stability

### Manufacturing precision

- High density interposers (organic/inorganic)

- Sub-micron alignment

- Controlling process variations

- Enabling stress-free bonding

- New testing concepts

#### **Standardization**

- Defining universal design rules

- Standardizing interfaces

- Ensuring process compatibility

- Establishing reliability benchmarks

### **Cost management**

- Reducing fabrication costs

- Improving yield

- Scaling automated assembly

- Minimizing supplier dependency

# Purpose of the APECS pilot line

- Position Europe's R&D and industry at the forefront of semiconductor innovation

- Establish a cutting-edge infrastructure for heterogeneous integration and chiplet technology

- Advance technological capabilities for cutting-edge semiconductor devices

- Support European industries (e.g., automotive, telecom, healthcare, IoT)

- Join forces with Europe's RTOs to accelerate technology transfer and enhance collaboration among

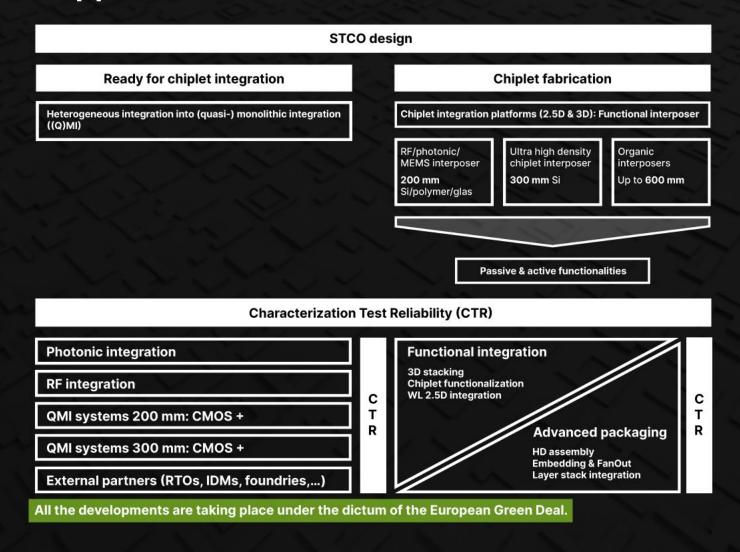

# APECS brings the connection between design, technology and testing for wide range of applications

# **Key innovation of the APECS pilot line**

- Worldwide first advanced automotive chiplet integration platform (2.5D and 3D) for multiple core technologies (CMOS, Opto/RF) and non-electronic devices (MEMS, Opto, OLED), leveraging the innovations of advanced packaging

- Comprehensive end-to-end design flow and methodology for chiplet-based advanced heterogeneous systems integration Design-for-Performance, -Yield, -Power Efficiency, -Testability

- Expansion of hetero-integration into quasimonolithic integration (QMI) for highest performance density by leveraging Back-End-of-Line and Advanced Packaging capabilities

- Prototyping of high performance chipletbased systems for specific needs of the European industries, in particular, automotive, medical device and health care, sensors and advanced manufacturing industries

- Novel backend-of-line interfacing technology for MEMS, opto/RF chips (III/V RF chiplets with (Bi)CMOS for 100 GHz+ frequencies)

- Novel testing concepts and technologies for function-, quality- and yield- optimization

# Potential for industrial uptake

#### Users

**Chip Foundries**

Integrated Device Manufacturer (IDMs)

Materials & Tools Supplier

Semiconductor Customer

**Research Community**

Start-ups

### **Value Proposition**

**Design Services:** enable chip, chiplet IP, and system design for APECS Pilot Line; provide and operate design platforms with support

Process development, materials and tool validation: accelerate technology development and validate processes for commercial transfer

**System Development:** leverage APECS tech for new products and business; enable access to specialized technologies

**Manufacturing Outsourcing:** offer Proof of Concept, prototype runs, small-volume production, and scalable transfer options

**Design Services:** enable chip, chiplet IP, and system design for APECS Pilot Line; provide and operate design platforms with support

**Research Access:** support research-to-application transfer; Provide easy access via local competence centers

### **Central point of Contact**

#### **APECS Business Office in Berlin**

c/o Fraunhofer-Verbund Mikroelektronik Anna-Louisa-Karsch-Str. 2 10178 Berlin Germany

### Prof. Dr. Albert Heuberger

Chairman of the FMD and Spokesman of the Fraunhofer Group for Microelectronics

Executive Director of the Fraunhofer Institute for Integrated Circuits IIS

+49 9131 776 1000 albert.heuberger@iis.fraunhofer.de

#### Coordinated by

#### Implemented by

#### **Pilot Line Project Partners**

#### Co-funded by

**APECS** is co-funded by the European Commission and national ministries of the eight member states within the framework of the EU Chips Act. Overall funding for APECS amounts to € 730 million over 4.5 years.

RÉPUBLIQUE FRANÇAISE